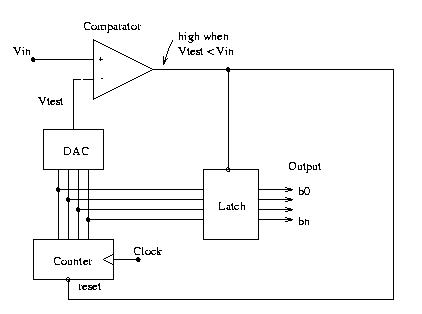

Counting ADC

The figure above illustrates the concept of the counting ADC. The counter starts at zero, thus the output of the digital to analog converter (DAC), Vtest, will also be zero. If Vin, the voltage to be converted to digital format, is some positive value, then Vtest < Vin, so the comparator output will start out high. The clock increments the counter, resulting in Vtest jumping up to some small positive value. If Vtest is still less than Vin, then the clock increments the counter again, which in turn increases Vtest again. This process continues until Vtest becomes greater than Vin. When that happens, the comparator output goes low. This triggers the latch to send data from its input side to its output, thus completing the conversion of the analog voltage Vin to digital format at the output of the latch. When the latch sends the data to its output, the counter is reset to zero, resulting in Vtest once again becoming less than Vin, and the comparator output goes high again. The counting ADC is then ready for another conversion.