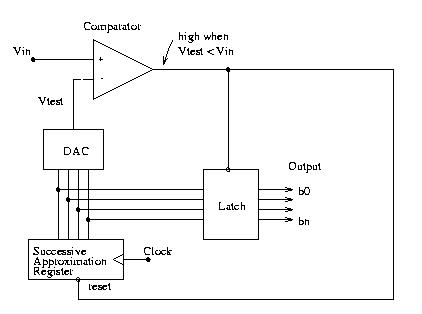

Successive Approximation Register (SAR) ADC

The successive approximation register (SAR) ADC is an improvement on the counting ADC. In this case, the counter on the counting ADC is replaced with a successive approximation register. The SAR does the A to D conversion more efficiently by first making the MSB a 1 then testing the output of the comparator to see if the output of the DAC is still smaller than the analog input voltage. If it still is smaller, then the next MSB is made a 1, and the test is repeated. On the other hand, if the output of the DAC is larger than the analog input, then the bit is changed back to zero, and the next MSB is made a 1 and the test is repeated.

By this method, the time to convert an analog voltage to digital is n clock cycles, where n = # of bits. Compare this to the conversion time of the counting ADC where the maximum possible time is 2n - 1 clock cycles.