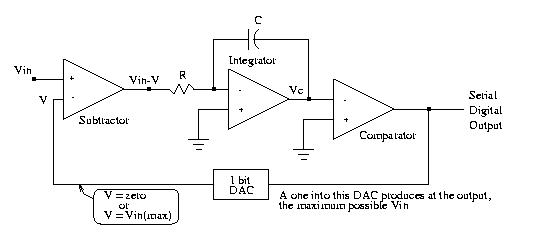

Sigma-Delta ADC

At t = 0, assume that the output of the digital to analog converter (DAC)

is zero, then if Vin = (1/2)Vin(max), Vc will be negative which makes the

comparator output high, which produces a Vin(max) at the output of the DAC,

which makes a negative input into the integrator, producing a positive Vc,

making the comparator output low, causing the output of the DAC to be zero,

and the cycle repeats as with t = 0. Similar analysis can be done with Vin =

0 and Vin = Vin(max). The results are as follows:

Vin = 0

=> Output = 000000...

Vin = (1/2)Vin(max)

=> Output = 101010...

Vin = Vin(max)

=> Output = 111111...

Thus, the higher the input voltage, the greater the prevalence of one's at the serial digital output.