Subranging Parallel Comparator (Subranging Flash) ADC

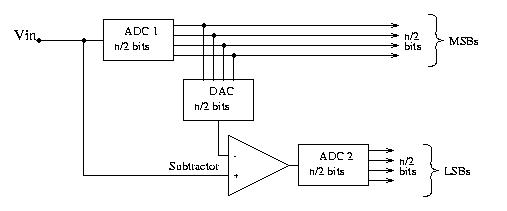

This method lets you make an n bit ADC using two n/2 bit ADCs. For example, an 8 bit flash ADC requires 28 - 1 = 255 comparators, whereas an 8 bit subranging flash ADC requires 2( 24 - 1 ) = 30 comparators. An n bit subranging flash ADC has the following architecture:

The output of the first ADC becomes the most significant bits (MSBs). This output is also converted back to analog with a digital to analog converter (DAC). The output of the DAC is subtracted from the original input voltage. The result of this subtraction represents the quantization error of the first ADC, which can be either positive or negative. This error goes into the second ADC to produce the least significant bits (LSBs) of the output, which amounts to a slight correction to the number represented by the MSBs.

To avoid errors at the output of the subtractor due to the input voltage changing faster than the propagation time through the first ADC and DAC, a sample and hold circuit should be used for the input.